Background

Recent advances in sensor technologies and growing capabilities of modern satellites have created significant demand for spacecraft data recording technologies which provide large storage capacities (on the order of terabits) and high-speed data interfaces (on order of gigabits per second). In the last several years, Southwest Research Institute has emerged as a major provider of advanced solid-state recorders (SSRs) for space applications, providing unique and powerful solutions for these demanding requirements. The flash memory technology that makes up the primary data storage medium of these SSRs is subject to a phenomenon known as bad blocks: isolated regions of memory which are unreliable at manufacture or become unreliable during operation. Proper functioning of an SSR requires bad block management: mechanisms to identify and record the locations of bad blocks and to avoid using those blocks for data storage. Previous SwRI SSRs have used software-based bad block management. In this approach, software algorithms are used to manage the bad blocks in the SSR rather than relying on the Field Programmable Gate Array (FPGA) in the SSR to perform this function. While attractive as a technical solution, there is increasing demand for SSRs that do not use software for bad block management. A bad block management capability implemented exclusively in programmable digital logic reduces the cost and power requirements of an SSR while simplifying integration within the larger space system.

Approach

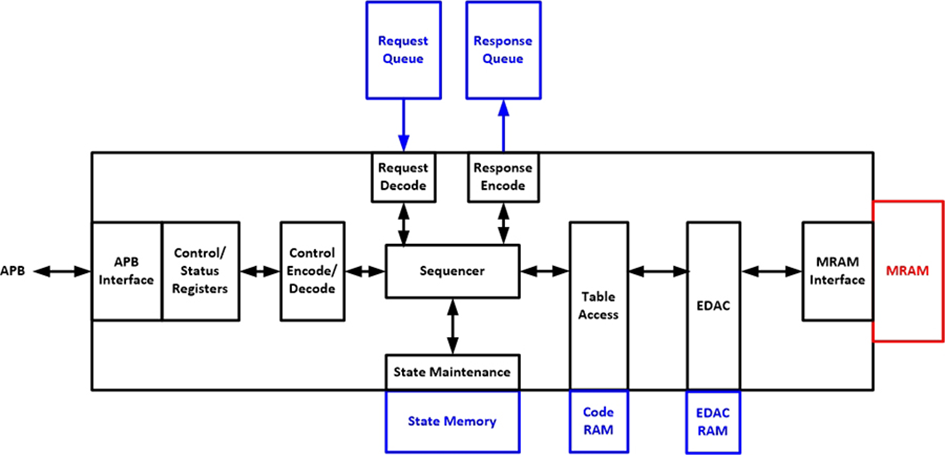

This project developed a capability to manage bad blocks within the programmable logic of the FPGA incorporated into the SSR. This approach can provide essential bad block management services without the additional design complexity of a dedicated processor and without the requirement that the host system execute a software solution. This research formulated a general framework for bad block management that can be directly employed on a wide variety of SSR architectures and satisfy diverse mission needs. The research developed a flexible memory addressing scheme which can be configured to support a wide variety of designs. The program also defined a set of abstract bad block management services to support high-speed data recording and playback as well as providing extensive status, maintenance, and diagnostic functions.

Accomplishments

This research produced a prototype implementation of the bad block management service which may be implemented within the programmable digital logic of an FPGA. This prototype implements the abstract addressing mechanism developed through the research and provides the full set of bad block management services identified. The implementation is highly configurable, enabling adaptation to address diverse SSR architectures using a small number of configuration values. Thorough simulation testing demonstrated that implementation can operate correctly with low response latency while using only a small fraction of FPGA resources.

Figure 1: Block diagram of the bad block manager, including interfaces to nonvolatile memory for table storage, abstract interfaces to data management logic for high-speed data recording and playback, and standardized interface for status, maintenance, and diagnostic functions.